|     | REVISIONS |                         |        |         |         |          |

|-----|-----------|-------------------------|--------|---------|---------|----------|

| DCN | LTR       | DESCRIPTION             | DATE   | CHANGED | CHECKED | APPROVED |

|     | 3         | PRELIMINARY             | 160718 |         |         |          |

|     | -         | RELEASED FOR PRODUCTION | 160720 |         |         |          |

|     |           |                         |        |         |         |          |

|     |           |                         |        |         |         |          |

|     |           |                         |        |         |         |          |

|     |           |                         |        |         |         |          |

# UNCONTROLLED COPY Contact AMI to verify revision

#### **RESTRICTED DATA**

THIS DRAWING CONTAINS INFORMATION DEEMED PROPRIETARY TO ANALOG MODULES, INC. AND IS TO BE USED ONLY FOR THE PURPOSE FOR WHICH IT IS SUBMITTED, AND FURTHERMORE, SHALL NOT BE COPIED IN WHOLE OR IN PART WITHOUT THE EXPRESS WRITTEN PERMISSION OBTAINED FROM ANALOG MODULES, INC.

|                                                           |                                                    |           | 16-031        | .doc             |              |                |      |        |     |      | -  | REV      |

|-----------------------------------------------------------|----------------------------------------------------|-----------|---------------|------------------|--------------|----------------|------|--------|-----|------|----|----------|

| UNLESS OTHERWISE SPECI-<br>FIED:<br>ALL DIMENSIONS ARE IN | a HEICO compan                                     |           | ANA           | LOG              | ON           | DU             | LE   | S      | ,   | IN   | C. |          |

| INCHES. ALL CAPACITANCE VALUES ARE IN MICROFARADS.        | DRAWN BY                                           |           |               | DATE             | CHECKED E    |                | D BY |        |     | DATE |    |          |

| ALL RESISTANCE VALUES ARE IN OHMS.                        | C. Smith                                           |           |               | 160720           |              |                |      |        |     |      |    |          |

|                                                           | LEAD APPROVAL                                      |           |               | DATE             |              | FINAL APPROVAL |      |        |     | DATE |    |          |

| TOLERANCES                                                | C. Smith                                           |           |               | 160720           | John Harwick |                |      | 160720 |     | 20   |    |          |

| DECIMAL<br>.XX = N/A<br>.XXX = N/A                        | OPERATING MANUAL MODEL 7612A OPTICAL SWITCH DRIVER |           |               |                  |              |                |      |        |     |      |    |          |

| ANGULAR<br>X = N/A                                        | SCALE<br>N/A                                       | SIZE<br>A | FSCM<br>61651 | SHEET<br>1 OF 11 | DRAW<br>NUMB |                | ,    | 16-0   | 031 | 1    |    | REV<br>- |

FILENAME

# **Table of Contents**

| LIST OF TABLES                                        | 3  |

|-------------------------------------------------------|----|

| LIST OF FIGURES                                       | 3  |

| LIST OF EQUATIONS                                     | 3  |

| INTRODUCTION                                          | 4  |

| SAFETY                                                | 4  |

| MOUNTING                                              | 4  |

| MOUNTING THE OPTICAL SWITCH                           | 4  |

| BEFORE POWERING UP                                    | 4  |

| ELECTRICAL INTERFACE                                  | 6  |

| J1 – MMCX JACK                                        | 6  |

| TB1 – INPUT POWER SCREW TERMINAL BLOCK                |    |

| P1 – ALTERNATE INPUT POWER CONNECTOR                  |    |

| JP1 – 8-PIN MICROMATCH RECEPTACLE                     |    |

| SW1 – TEC DISABLE SWITCH                              | 6  |

| INPUTS                                                | 7  |

| +5 POWER                                              | 7  |

| Power Ground                                          |    |

| CURRENT CONTROL INPUT                                 |    |

| ENABLE                                                | 7  |

| OUTPUTS                                               | 7  |

| TEMP FAULT                                            | 7  |

| OVER CURRENT                                          | 8  |

| SETTINGS AND ADJUSTMENTS                              | 8  |

| TEC TEMPERATURE SETTING                               | 8  |

| CURRENT LIMIT ADJUST                                  |    |

| Preliminary Offset                                    |    |

| FINAL OFFSET AND BIAS CURRENT                         | 9  |

| TEC CONTROLLER MAXIMUM CURRENT AND VOLTAGE PARAMETERS | 9  |

| Max voltage                                           | 9  |

| Max current                                           |    |

| ROADD OUTLINE AND DIMENSIONS                          | 11 |

# **List of Tables**

|      | TABLE 1 – ADJUSTABLE PARAMETERS AND METHOD OF ADJUSTMENT      | 5 |

|------|---------------------------------------------------------------|---|

|      | TABLE 2 – J2 PIN DESCRIPTION                                  | 7 |

|      | TABLE 3 – OPTICAL SWITCH 14-PIN BUTTERFLY PACKAGE PINOUT      | 7 |

| List | of Figures                                                    |   |

|      | FIGURE 1 – ADJUSTMENT POTENTIOMETERS                          | 5 |

|      | FIGURE 2 – INPUT/OUTPUT AND POWER CONNECTORS                  | 6 |

|      | FIGURE 3 – ADJUSTMENT POTENTIOMETERS AND MEASUREMENT POINTS 1 | 0 |

| List | of Equations                                                  |   |

|      | EQUATION 1 – THERMISTOR RESISTANCE TO VOLTAGE                 | 8 |

|      | EQUATION 2 – CURRENT LIMIT SET POINT VOLTAGE                  | 8 |

|      | EQUATION 3 – R71 VALUE CALCULATION                            | 9 |

|      | EQUATION 4 – R70 VALUE CALCULATION                            | 9 |

## Introduction

The Model 7612A Optical Switch Driver is a high performance general purpose OEM driver. The driver uses a 14 pin butterfly packaged module with a common industry pinout supported by several manufacturers.

The driver is optimized for lower current driver output (less than 1.0A) however; operation up to 1.2A is possible for average powers less than 1Watt or 1.25W with ≥200LFM forced air cooling. It is implemented as a transconductance amplifier (analog voltage in, scaled current out).

The driver circuitry operates from a single +5VDC power source. All other needed voltages are generated on the board by high efficiency switching power supplies.

The driver supplies a bidirectional PID switching TE cooler controller with current capability to ±3A and voltage capability to ±4V.

## Safety

The driver does not generate or use any hazardous voltages, so high voltage precautions are not required in mounting or use. Keep work areas policed up of fiber fragments and off trims. Safe disposal of these is very important to avoid injury.

## Mounting

The driver is normally shipped without an optical switch installed. The first step is to determine the worst case use parameters. For all but the very lowest power applications, a heat sink will be required. Determine the power dissipated in the switch, and TE cooler. Most TE coolers cannot hold the temperature with a differential from die to heat sink much over 45°C. Generally that is the requirement which determines the specifications for the heat sink attached to the unit mounting flange and any need for forced air, etc. The drive FETS and TEC controller dissipate their heat into the PC board. Use heatsink grease or other thermally conducting medium on the heat transfer surfaces of the optical switch. The switch connections to the board will have to bear the mechanical load of either the PCB or the heatsink. To avoid this strain the board and the heatsink should be screwed together, or each should be mounted to a third support.

## **Mounting the Optical Switch**

See Table 3 for acceptable pinout. To minimize mounting stress the following procedure should be followed:

- 1. If the board is being mounted with standoffs, screw to heat sink, but do not tighten.

- 2. Place the optical switch through the hole in the board, and insert the mounting screws in all corners. Leave loose.

- 3. Move the board around as needed to align the pins with the solder pads. Tighten the board mounting screws.

- 4. Carefully trim the pins to fit on the pads. Removing the optical switch from the PCB may make this easier.

- 5. When the pins have been trimmed and passed a trial fit, coat the bottom of the switch with heat transfer material, and screw down to the heat sink.

- 6. Solder the leads to the pads.

## **Before Powering Up**

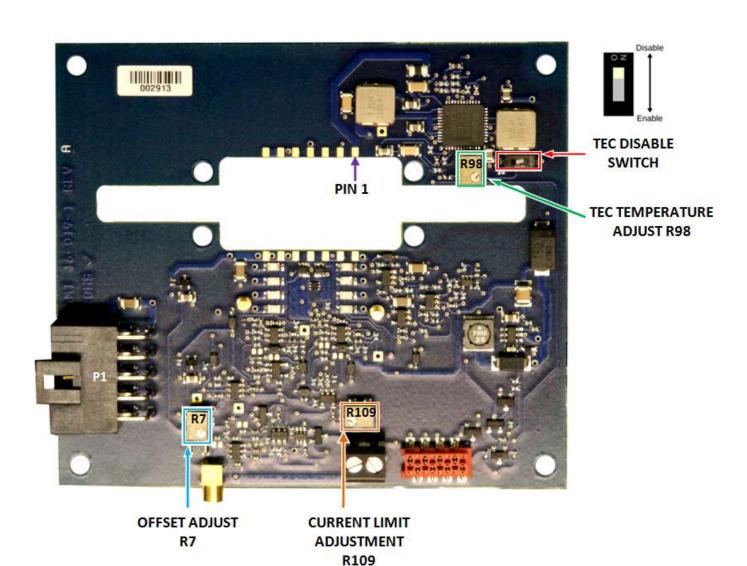

Review Table 1 against the specifications for the optical switch to determine if pre-turn on adjustments should be made to the driver. Most of the adjustments must be made with the power on, so for the present simply turn the control pot in the indicated direction at least 5 turns. See Fig. 1 for potentiometer locations.

DWG#: 16-031 REV: -FILE#: 16-031.doc DATE: 160719

DCN#:

| Adjustment           | Factory Setting | Pot  | Turn Pot to Lower Setting |

|----------------------|-----------------|------|---------------------------|

| TEC Temperature      | 25°C.           | R98  | CCW                       |

| Offset Adjust        | +1mV(~2mA)      | R7   | CCW                       |

| Current Limit Adjust | 2.11V (1.1A)    | R109 | CCW                       |

| TEC Max Voltage      | 3.14V           | R73  | Fixed Resistor            |

| TEC Max Current      | 1.8A            | R74  | Fixed Resistor            |

TABLE 1 – ADJUSTABLE PARAMETERS AND METHOD OF ADJUSTMENT

FIGURE 1 – ADJUSTMENT POTENTIOMETERS

## **Electrical Interface**

The model 7612A connections, signals, and signal behavior are described here.

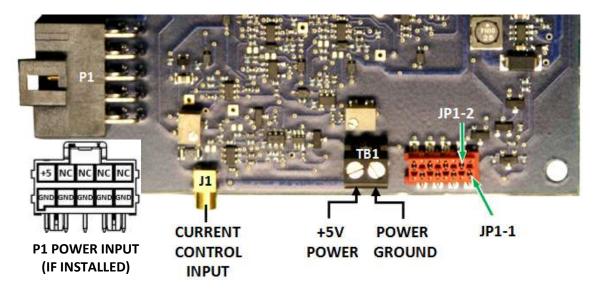

FIGURE 2 - INPUT/OUTPUT AND POWER CONNECTORS

#### J1 - MMCX Jack

J1 is a miniature 50  $\Omega$  MMCX jack that mates with a straight or right angle MMCX plug and 50  $\Omega$  coaxial cable assembly.

#### TB1 - Input Power Screw Terminal Block

The screw terminal block accepts between 16 AWG to 28 AWG wire for driver power and ground.. All connection locations are shown in Figure 2.

#### P1 - Alternate Input Power Connector

P1 is not installed on the standard 7612A.

#### JP1 - 8-pin MicroMatch Receptacle

JP1 mates with a keyed 8-pin MicroMatch IDC style header connected to 8-position, 28 AWG ribbon cable. The JP1 pin descriptions and locations can be found below in Table 2 for further clarification.

#### SW1 - TEC Disable Switch

A surface mounted switch SW1 can be used to disable the TEC regardless of temperature.

| I/O CONNECTOR Pinout |              |  |  |  |

|----------------------|--------------|--|--|--|

| JP1                  |              |  |  |  |

| Pin                  | Function     |  |  |  |

| 1                    | Enable       |  |  |  |

| 2                    | GND          |  |  |  |

| 3                    | Temp Fault   |  |  |  |

| 4                    | GND          |  |  |  |

| 5                    | Over Current |  |  |  |

| 6                    | GND          |  |  |  |

| 7                    | N/C          |  |  |  |

| 8                    | GND          |  |  |  |

| <b>Optical Switch Pinout</b> |             |  |  |

|------------------------------|-------------|--|--|

| Pin                          | Function    |  |  |

| 1                            | TEC +       |  |  |

| 2                            | Thermistor  |  |  |

| 3                            | N/C         |  |  |

| 4                            | N/C         |  |  |

| 5                            | Thermistor  |  |  |

| 6                            | N/C         |  |  |

| 7                            | N/C         |  |  |

| 8                            | N/C         |  |  |

| 9                            | N/C         |  |  |

| 10                           | Anode       |  |  |

| 11                           | Cathode     |  |  |

| 12                           | N/C         |  |  |

| 13                           | Case Ground |  |  |

| 14                           | TEC -       |  |  |

**TABLE 2 – JP1 PIN DESCRIPTION**

TABLE 3 –14-PIN BUTTERFLY PACKAGE PINOUT

## **Inputs**

#### +5 Power

Driver power should be +5V±0.25V, up to 3A. Voltage levels apply at the board input terminals under minimum to maximum loads.

#### **Power Ground**

This is the return line for the input power. Size wiring run accordingly.

#### **Current Control Input**

This is an analog input. The input impedance is  $50\Omega$ . The switch current is scaled to the input voltage at 0.333 A/V, not to exceed 4.5V. The current will follow the control input thru any modulation waveform within the bandwidth of the driver. The driver bandwidth is approximately 50MHz. The input voltage is offset by the offset control and limited by the current limit control.

#### Enable

This input is compatible with TTL, 3.3V and 5V CMOS logic, open drain or collector switches, and mechanical switches and relays. The input is pulled up to +5V with a 10K resistor. If 3.3V CMOS is used to drive it connect a 15K resistor from the input to ground to protect the driving logic from over voltage. Any input value which lowers the voltage at the Enable input below 0.4V will enable the driver. This includes logic outputs, or simply shorting to ground. Any time the input voltage is above 2.4V, the optical switch will be disabled. This includes logic outputs, or open circuiting the input. Between 0.4 and 2.4V the state is indeterminate.

## **Outputs**

#### Temp Fault

This signal is active low, and asserts whenever the driver has been disabled by the temperature monitoring system. The signal is open drain with an internal 4.75K pull up to +5V. The signal is capable of driving TTL, 3.3 and 5V CMOS, sensitive relays, transistors, FETs, and LEDs. The application will determine which devices are appropriate. If the output is being used to drive 3.3V CMOS, install a 6.8K resistor from output to ground to

prevent over voltage on the logic input. The maximum sink load should be limited to 25mA.

This signal can be asserted by two separate causes. First, it will be asserted whenever the optical switch temperature is outside a window of approximately ±1 degree from the set point temperature. Second, the signal will be asserted when the switch current driving FETs junction temperature exceeds approx 125°C. Both of these causes will disable the driver while the FETs cool below 125°C, or the TEC controller regains control of the die temperature. The source of the shutdown can be identified by noting the "off" time. It will be seconds for a TEC controller shutdown, and milliseconds for a FET shutdown. If the TEC controller is shutting down, Reduce the load or ambient temperature, or increase the heat sinking for the optical switch. If it's a FET shutdown, reduce the load or ambient temperature, or add a cooling fan for the PCB. It is not recommended that the unit be operated in a manner that causes repeated temp faults.

#### **Over Current**

This signal is active low. It is asserted when the current limiting circuits are clipping the input signal. The signal is open drain with no internal pull up to +5V. The signal is capable of driving TTL, 3.3V and 5V CMOS, sensitive relays, transistors, FETs, and LEDs. The application will determine which devices are appropriate. The user may insert the load between the output and some positive voltage ≤12V for current operated loads like LED's and relays. An external pull-up resistor will be required to drive voltage operated loads like transistors and logic inputs.

### **SETTINGS AND ADJUSTMENTS**

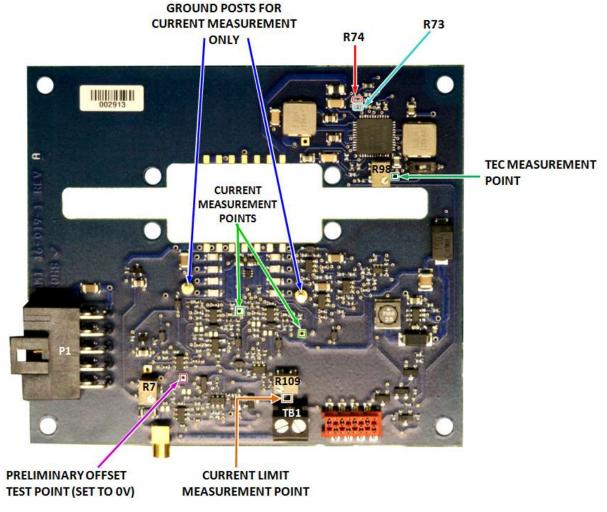

Check Table 1, any setting which has been set by the factory to the values required for the application, can be skipped in what follows. See Table 1 for a list of adjustable parameters and their settings. Those parameters which can be adjusted by potentiometers will be dealt with first. To make these adjustments, the user will need a voltmeter with 1% basic accuracy and 0.1mV resolution for voltages below 0.4V. See Figure 3 for probe points for each adjustment. Ground meter or scope at input connector for all but the current measuring. For this, use the post grounds for each of the current test points. These grounds give effectively a differential measure across the sense resistors.

#### **TEC Temperature Setting**

Different manufacturers use different thermistors in their products. Although, 10K value at +25°C is the most common value and is what the controller circuitry is designed for, the thermistor curves are not identical. To assure accurate temperature settings a chart of resistance vs. temperature is needed for the thermistor in question. Look up the value at the desired operating temperature, and use the formula below to determine the measurement point voltage for that thermistor resistance. Adjust the measured voltage to the calculated value.

$$V_{set} = \frac{1.5 * R_{th}}{(R_{th} + 10000)}$$

#### **EQUATION 1 - THERMISTOR RESISTANCE TO VOLTAGE**

#### **Current Limit Adjust**

Determine the desired setting of limiting current. Use the following formula to determine the set point voltage at the current limit measurement point:

$$V_{set} = Current\ Limit * 1.918$$

**EQUATION 2 - CURRENT LIMIT SET POINT VOLTAGE**

#### **Preliminary Offset**

Adjust for 0 volts at the measurement point.

#### Final Offset and Bias Current

This setting must be made with the optical switch enabled. The current calibration at the measurement point is 1mA/mV. Adjust for the desired DC bias current. There are two measurement points and their corresponding grounds. The current is the sum of the two. Should the desired current be 0, approach the final setting from a few millivolts positive and stop turning as soon as the voltage at the test point stops moving. The voltage can't be reduced at the test point any further, but if the adjustment is turned more negative, the current pulse will be clipped, and will not reach its full value based on the scale (0.333A/V).

If it is desired to use a digital signal into the input, the bias can be offset negative to accommodate the logic "0" voltage of the source. Put the logic "0" signal in and adjust for the desired bias current. If the logic "0" stability vs. power supply, or temperature is not adequate, use an emitter follower to drive the input. When turned off, the 50 Ohm input resistor will drag the input down to a few micro volts. Set the Current Limit to the actual value of current (see above) you desire, and it will clip the Logic "1" level to the appropriate value. In this configuration an "over current" output pulse will be produced for each input pulse.

## TEC Controller Maximum Current and Voltage Parameters

Should these parameters need to be reset from the factory settings for a particular device, proceed as follows:

#### Max voltage

Determine the maximum required. This can be set no higher than 4.3V. Use the following equation to determine the value to install for R73.

$$R73 = \frac{60000 - (10000 * V_{TEC})}{V_{TEC}}$$

**EQUATION 3 - R73 VALUE CALCULATION**

#### Max current

Determine the maximum required. This can be set no higher than 3A. Use the following equation to determine the value to install for R74.

$$R74 = \frac{2.6 \times 10^5 * I_{TEC}}{50 - 13 * I_{TEC}}$$

**EQUATION 4 – R74 VALUE CALCULATION**

FIGURE 3 – ADJUSTMENT POTENTIOMETERS AND MEASUREMENT POINTS

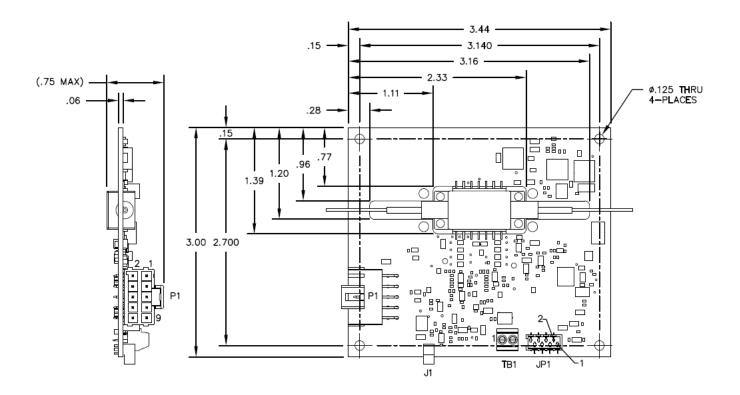

# **Board Outline and Dimensions**